Investigation of a USRP FPGA Platform for Quantum Sensing and Control

Aaron Wubshet

|            | Background            |

|------------|-----------------------|

| <u></u>    | Algorithm development |

|            | Hardware Realization  |

| *          | Conclusion            |

| <b>!</b> ! | Next Steps            |

| ?          | Questions             |

# Logistics & Scope

FEASIBILITY STUDY FOLLOW UP TO LDRD POSTER SESSION, SEMINAR, AND MASTER'S THESIS

USRP PLATFORM FOR SUPERCONDUCTING QUANTUM SENSING Lawrence Livermore Aboratory Directed Aaron Wubshet, John Breneman, Lisa Poyneer

National Laboratory

#### **BACKGROUND & APPLICATIONS**

- DOE National Strategic Computing Initiative and LLNL's HPC, Simulation, and Data Science core competency

- We want to rapidly control a superconducting qubit

- Desirable output

- Axion detection research

- Quantum information processing

MATLAB

Leverage and adapt

Simulate and validate

functional behavior via

existing IP

testbench

• Design:

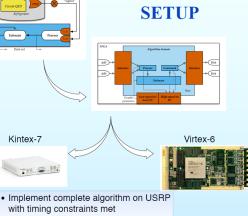

June • Migrate "process" onto USRP Begin investigating universal portability of HDL generated ..... **Progress** • Synthesis: Resource utilization determined Netlist generated

Place & Route:

generated

Timing constraints

Programming file

**EXPERIMENTAL**

Dec.

- with timing constraints met Finalize thesis project experiment

- Sept. Gather materials & relevant

- Combining multiple toolchains into cohesive workflow

- portability of HDL being generated

toolchains required

analysis, & thesis

Complete data collection,

• Validation of USRP implementation

under the auspices of the U.S.Department of Energy by Lawrence Livermore National Laboratory under ContractDE-AC52-07NA27344 and was supported by the LLNL-LDRD Program under Project No.17-ERD-006. IM RELEASE NUMBER: LLNL-POST-78228

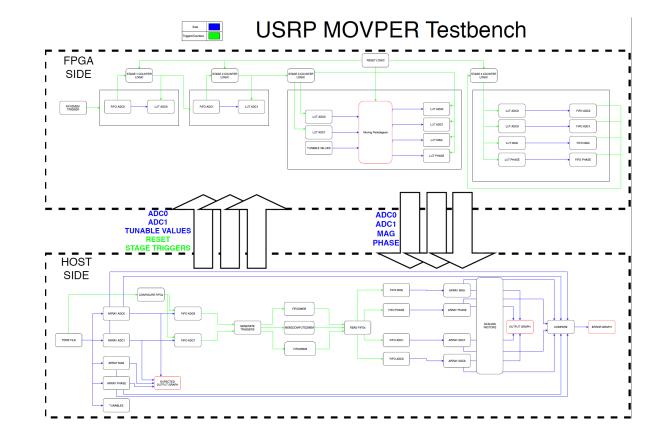

- Unique testbench for USRP platform

- Additional handshaking required

### **NEXT STEPS**

MIT 6-A M.Eng

#### CURRENT PROJECT

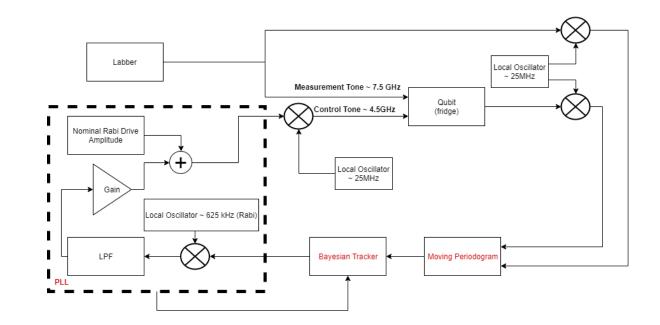

- The goal is to develop and experimentally validate algorithmic, FPGA-based control of a transmon

- Current progress is concentrated on II FPGA, but migration to USRP (and other platforms) is underway

- Modify implementation in order to meet timing requirements

#### POSSTBLE THESTS EXPERIMENTS

- Implement less computationally intensive control scheme on FPGA (PID, state space, etc)

- Implement processing, control, and estimation in native VHDL to ensure portability

- Created VHDL "wrapper" to enable Validate and characterize SDR capabilities relative to existing testing RF equipment

#### **Acknowledgements & References**

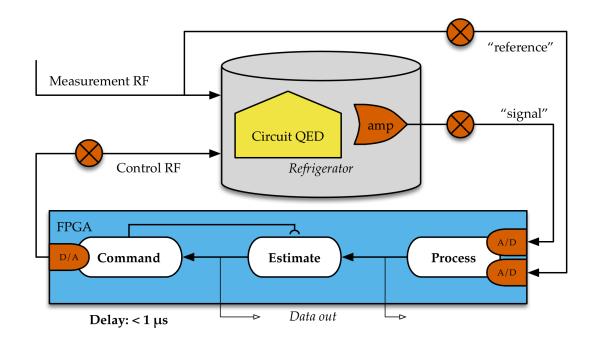

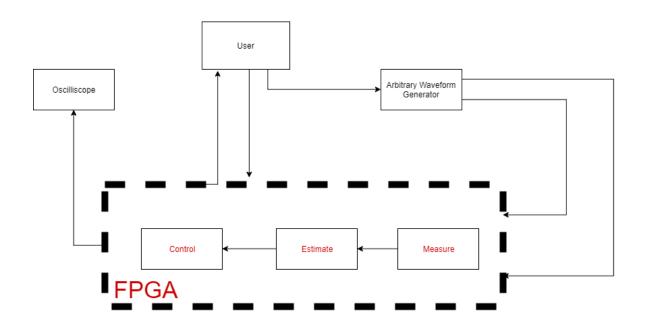

### Experimental Apparatus

- ➤ 4mK refrigerator

- Circuit QED = superconducting charge qubits as transmons

- External heterodyne

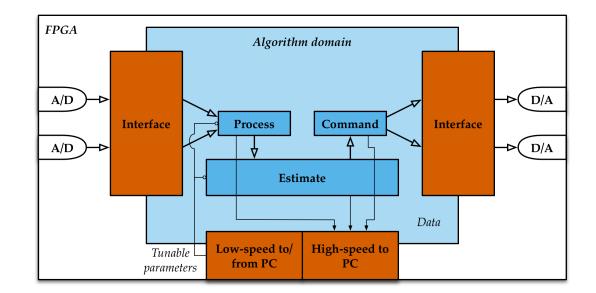

### FPGA Interface

- Defining interface for USRP

- Interacting with LabVIEW host

- Configuring RF peripherals

# Development Workflow

Simulation Benchtop Testing Laboratory Testing Data Analysis

# **XILINX**<sub>®</sub>

# Quantum Sensing and Control Algorithm (QSCA)

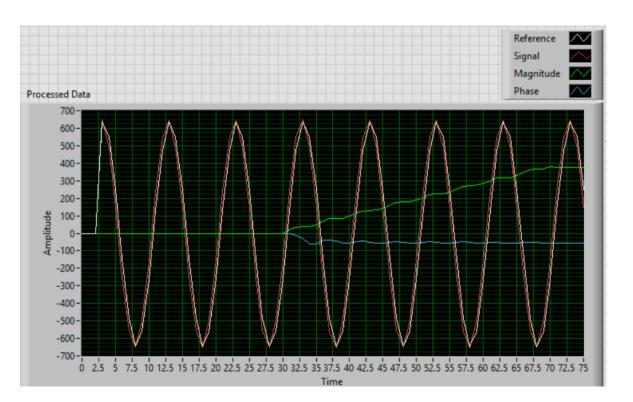

### Process

....

- Moving periodogram algorithm

- CORDIC block to provide phase and magnitude

- Phase difference detection

e

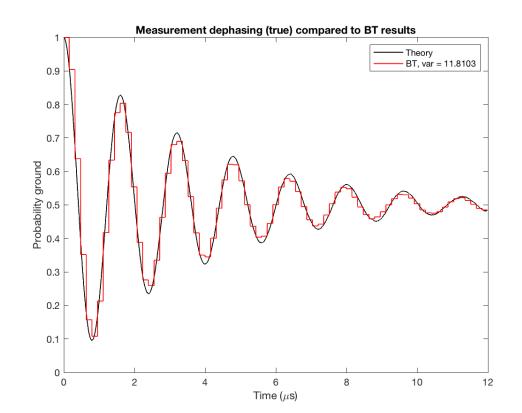

### Estimate

- State space model based approach

- Statistical Bayesian update

- Minimum update time 160ns

### Command

- Lock onto Bayesian Tracker estimate trajectory via mixing phase compensated local oscillator

- Low pass filter to extract signal proportional to phase difference

- Apply gain

ô

### HDL Coder

#### Critical Path Report for hdl\_all/QC\_HDL

#### Summary Section

Critical Path Delay : 8.902 ns Critical Path Begin : *HDL\_BT\_RM.* Critical Path for *i : Unit Delays.* Highlight Critical Path: C:\Users\wubshet1\Documents\hdlcoder\92519\_PRI\hdlsrc\hdl\_all\riticalPathEstimated.m Highlight Uncharacterized blocks: C:\Users\wubshet1\Documents\hdlcoder\92519\_PRI\hdlsrc\hdl\_all\highlightCriticalPathEstimationOffen

#### **Critical Path Details**

| Id | Propagation (ns) | Delay (ns) | Block Path       |

|----|------------------|------------|------------------|

| 1  | 8.9020           | 8.9020     | HDL_BT_RM        |

| 2  | 0.2980           | -8.6040    | Unit Delay1      |

| 3  | 8.8720           | 8.5740     | 1-D Lookup Table |

| 4  | 8.9020           | 0.0300     | Unit Delay5      |

- Generates customized VHDL to match Simulink functionality

- Pipelines to meet desired clock speed

- Modularizes VHDL libraries to mimic Simulink reference models

- Supports useful features in Simulink like data dictionaries

- Provides optimized blocks for certain operations

### II vs USRP

### ≻250MHz

- Depreciated drivers

- ISE generated bit file

- Interact with LabVIEW host with external C++ Library

- Interface requires modifications in VHDL

### ≻200MHz

- Modern platform

- Vivado generated bit file

- Interact with LabVIEW host with purely native LabVIEW code

- Interface requires minimal VHDL modifications, mostly defined and configured in LabVIEW

###

### Hello World

### Moving Periodogram Testbench

### **Full QSCA Testing**

### Hello World

- Blinking LEDs

- Simple data processing and transfer

- Exploring how to interact with radio front end

NI LabVIEW for CompactRIO Developer's Guide

Recommended LabVIEW Architectures and Development Practices for Control and Monitoring Applications

> SOFTWARE DEFINED RADIO HANDS ON: FPGA PROTOTYPING WITH OVER-THE-AIR SIGNALS

Version 4.0

NI LabVIEW High-Performance FPGA Developer's Guide

Recommended Practices for Optimizing LabVIEW RIO Applications

### Moving Periodogram Testbench

- Using data collected and validated on the II as input to validate

- Moving periodogram

- > Data transfer

- Using real AWG signals as stimulus

### Full QSCA Testing

- Trigger source, AWG, scope, and USRP set up to mimic laboratory experimental apparatus

- Data processed and saved by updated LabVIEW host

# Conclusion

The USRP *might* be a viable FPGA platform for quantum sensing and control and should be explored for quantum information research as well as axion detection research

## Next Steps

!

COMPLETE DATA COLLECTION/ANALYSIS COMPLETE THESIS

CODE REVIEW/HANDOFF

- Closed loop control

- Full state feedback